### A Brief Tour of FireSim: The Manager & Compiler; Building an FPGA image

https://fires.im

**ISCA 2021 Tutorial**

Speaker: Sagar Karandikar

#### Agenda: What will we cover?

- 1) The Compiler  $\rightarrow$  Golden Gate

- Invoke it on example RTL

- "Simulate the simulator" using Verilator

- 2) The Manager  $\rightarrow$  firesim

- Explain how it's configured

- Demonstrate how it's used to build bitstreams

#### Where is FireSim in Chipyard?

With the software RTL simulators!

~/chipyard/sims/firesim

→ We will reference this as \$FDIR

```

$ cd $FDIR

```

\$ 1s

### FireSim's Directory Structure

#### sim/

- Golden Gate lives here

- Scala & C++ sources for additional FireSim models

- Make-based build system to invoke Golden Gate

#### deploy/

- Manager lives here

- FireSim workload definitions

platforms/ → AWS FPGA/Vivado project definitions

sw/ → target software & FireMarshal (more on this later)

#### Agenda: What will we cover?

- 1) The Compiler → "Golden Gate"

- Invoke it on example RTL

- "Simulate the simulator" using Verilator

- 2) The Manager → firesim

- Explain how it's configured

- Demonstrate how it's used to build bitstreams

```

$ cd $FDIR/sim

```

\$ make DESIGN=FireSim

#### An Analogy

Golden Gate is like Verilator but for FPGA-accelerated simulation

Verilator generates C++ sources to simulate your design.

→ Compile and run on a CPU-host

Golden Gate generates C++ & Verilog to simulate your design.

→ Compile and run on a hybrid CPU & FPGA host

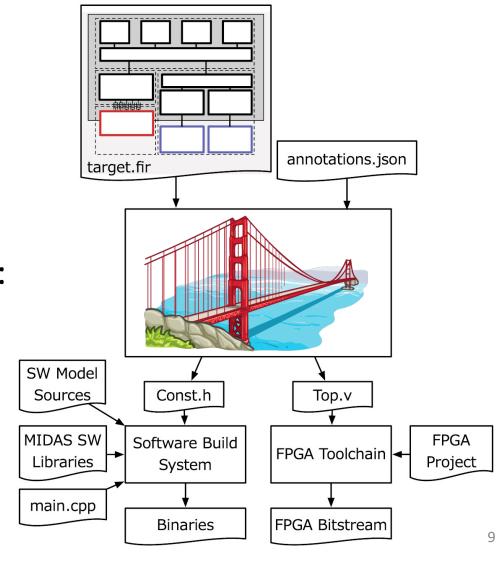

### Golden Gate Compiler

#### Inputs:

- FIRRTL & annos from a Chipyard generator

- Compiler configuration

- → Produces sources for a simulator that are:

- deterministic

- support co-simulation of software models

- area-optimized to fit more on the FPGA

#### Plug: ICCAD 2019 Publication

# GOLDEN GATE: Bridging The Resource-Efficiency Gap Between ASICs and FPGA Prototypes

Albert Magyar, David Biancolin, John Koenig, Sanjit Seshia, Jonathan Bachrach, Krste Asanović

#### Punchline:

- $\rightarrow$  Can fit two more BOOM cores (4 -> 6)

- → think: "-Os for FireSim"

#### Interacting with Golden Gate via Make

Make invokes Golden Gate with three variables (the "Tuple"):

#### **DESIGN:**

The top level module

MODEL in Chipyard

#### TARGET\_CONFIG:

The generator's config → CONFIG in Chipyard

#### PLATFORM\_CONFIG:

Compiler options passed to Golden Gate

```

$ cd $FDIR/sim/generated-src/f1

# here you'll find output directories for all builds

$ cd <any-directory-here>

$ ls

```

#### Inspecting the Outputs

```

<long-name>.fir & <long-name>.anno.json

```

Target's FIRRTL & annotations

```

FPGATop.v

```

The compiled simulator

```

$DESIGN-const.h

```

Simulator's memory map

```

runtime.conf

```

A default runtime configuration for simulation

#### Agenda: What will we cover?

- 1) The Compiler → Golden Gate

- Invoke it on example RTL

- Simulate the output in an RTL simulator

- 2) The Manager  $\rightarrow$  firesim

- Explain how it's configured

- Demonstrate how it's used to build bitstreams

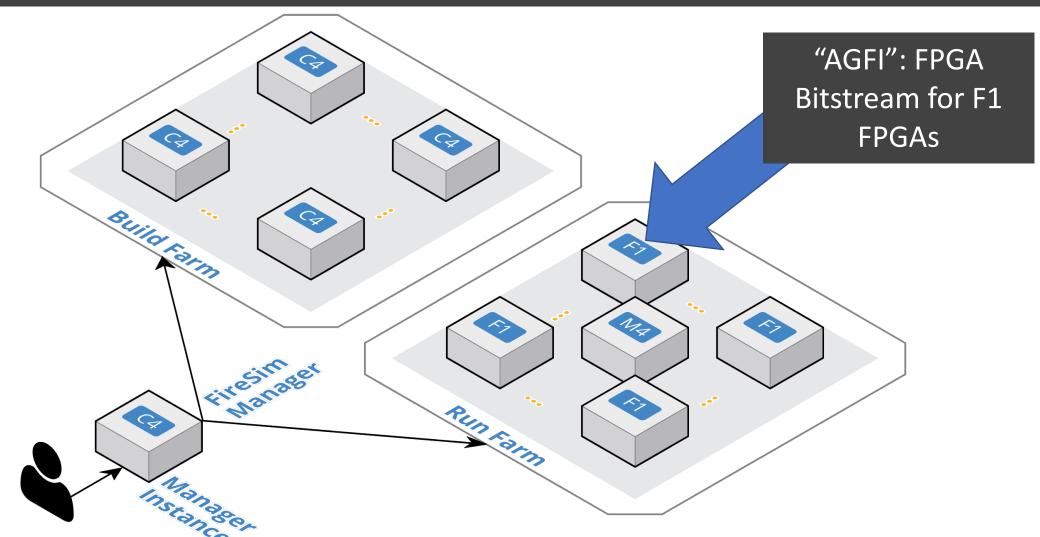

### Background Terminology

### Using the firesim manager command line

- sourcing \$FDIR/sourceme-f1-manager.sh puts firesim on your path

- can call firesim from anywhere on the instance

- it will always run from the directory:

\$FDIR/deploy/

After a fresh clone, need to call:

firesim managerinit

```

$ cd $FDIR/deploy

```

\$ 1s

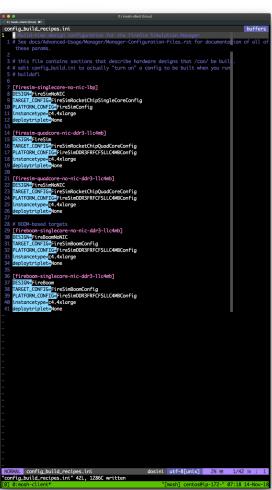

#### Configuring the Manager. 4 files in firesim/deploy/

config build recipes.ini

config build.ini

config\_hwdb.ini

```

config_hwdb.ini

# If you are using an older version of FireSim, you will need to generate you

resim-quadcore-nic-ddr3-llc4mb]

i=agfi-030b49bce9bd5ef96

NORMAL config_hwdb.ini

"config_hwdb.ini" 36L, 1131C written

dosini utf-8[unix] 2% ≡ 1/36 ln :

```

config runtime.ini

```

config_runtime.ini

defaulthwconfig=firesim-quadcore-no-nic-ddr3-llc4mb

NORMAL config_runtime.ini

"config_runtime.ini" 35L, 783C written

dosini utf-8[unix] 2% ≡ 1/35 ln :

```

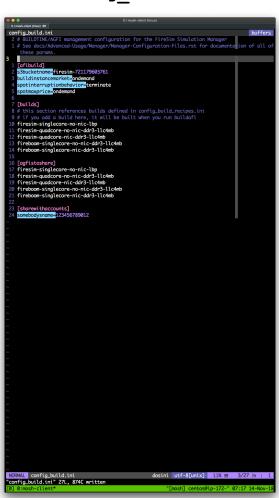

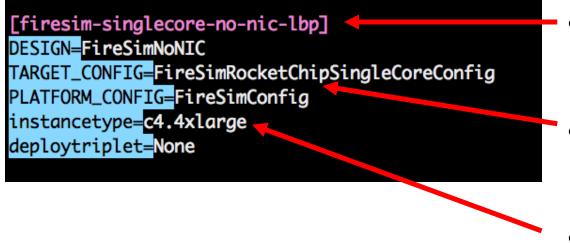

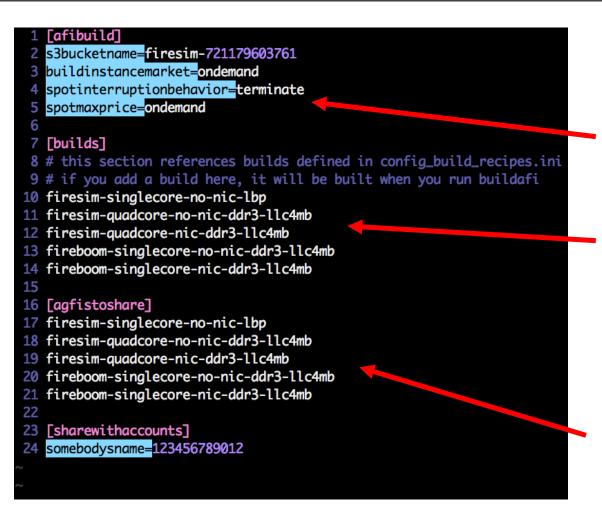

#### Configuring a Build

```

0 / mosh-client (tmux)

0 / mosh-client (tmux) #1

confia_build.ini

buffers

2 # BUILDTIME/AGFI management configuration for the FireSim Simulation Manager

1 # See docs/Advanced-Usage/Manager/Manager-Configuration-Files.rst for documentation of all of

these params.

[afibuild]

2 s3bucketname=firesim-721179603761

3 buildinstancemarket=ondemand

spotinterruptionbehavior=terminate

5 spotmaxprice=ondemand

7 [builds]

8 # this section references builds defined in config_build_recipes.ini

9 # if you add a build here, it will be built when you run buildafi

10 firesim-singlecore-no-nic-lbp

11 firesim-quadcore-no-nic-ddr3-llc4mb

12 firesim-auadcore-nic-ddr3-llc4mb

13 fireboom-singlecore-no-nic-ddr3-llc4mb

14 fireboom-singlecore-nic-ddr3-llc4mb

16 [agfistoshare]

17 firesim-singlecore-no-nic-lbp

18 firesim-quadcore-no-nic-ddr3-llc4mb

19 firesim-quadcore-nic-ddr3-llc4mb

20 fireboom-singlecore-no-nic-ddr3-llc4mb

21 fireboom-singlecore-nic-ddr3-llc4mb

23 [sharewithaccounts]

somebodysname=123456789012

```

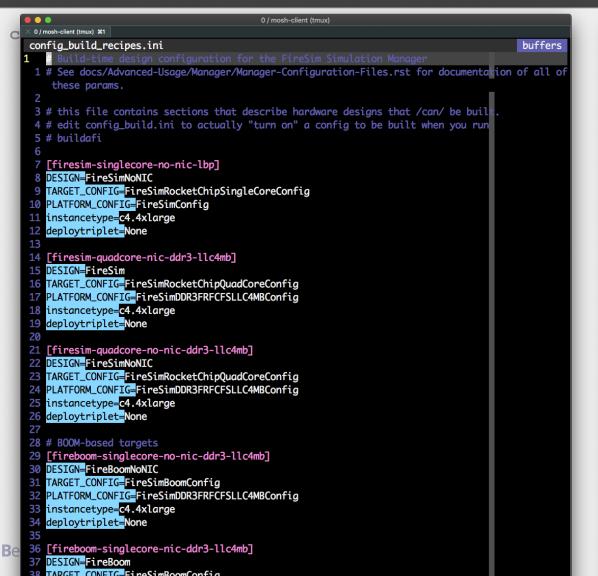

### Anatomy of a Build Recipe

#### Consists of:

A label

The tuple from before

• The EC2 instance type you'd like to use

## Defining a Build Job: config\_build.ini

#### Consists of:

More instance configurations

A list of recipes you'd like to batch out to a build farm

Once you're done with builds:

A list of recipes you'd like to share with other users

### Running builds

Once we've configured what we want to build, let's build it

\$ firesim buildafi

- This completely automates the process. For each design, in-parallel:

- Launch a build instance

- Generate target RTL & invokes Golden Gate

- Ship infrastructure to build instances, run Vivado FPGA builds in parallel

- Collect results back onto manager instance

- \$FDIR/deploy/results-build/<TIMESTAMP>-<tuple>/

- Email you the entry to put into config\_hwdb.ini

- Terminate the build instance

AWS Notifications <no-reply@sns.amazonaws.com>

to me 🔻

Your AGFI has been created!

Add

[firesim-singlecore-sha3-l2-no-nic-ddr3-llc4mb]

agfi=agfi-0679d5d17ba885886

deploytripletoverride=None

customruntimeconfig=None

to your config\_hwdb.ini to use this hardware configuration.

```

$ cd $FDIR/deploy

$ cd results-build/<name>/cl_firesim

$ ls

```

#### Captured Build Outputs

design/

The source files for the build;

build/scripts/<timestamp>.vivado.log

Log of the entire vivado build process

build/reports/

Timing and utilization reports from various stages

build/checkpoints/

Design checkpoints (\*.dcp); can reopen in Vivado to debug a build

```

$ cd $FDIR/deploy

$ cat built-hwdb-entries/* >> config_hwdb.ini

$ tail config_hwdb.ini

```

### Anatomy of a HWDB Entry

[fireboom-singlecore-no-nic-ddr3-11c4mb]

agfi=agfi-0df9101df7b7ff708

deploytripletoverride=None

customruntimeconfig=None

Same label as before

The FPGA image

Hooks to change:

Software models

Runtime arguments

→ Without FPGA recompilation

### Simulating the Simulator

Can simulate Golden Gate's output without doing an FPGA-build

Runs with all the same models you'd have on the FPGA

- Should produce target-cycle-exact behavior as an FPGA simulation

- → outputs in output/f1/<tuple>

#### Summary

- Don't fret if you didn't catch everything, everything we showed you today is documented in excruciating detail at <a href="http://docs.fires.im">http://docs.fires.im</a>

- We learned how to:

- Build FireSim FPGA images for a set of targets

- http://docs.fires.im/en/latest/Building-a-FireSim-AFI.html

## Backup Slides