# **Chipyard Framework Overview**

Jerry Zhao UC Berkeley jzh@berkeley.edu

Berkeley Architecture Research

Berkeley Architecture Research

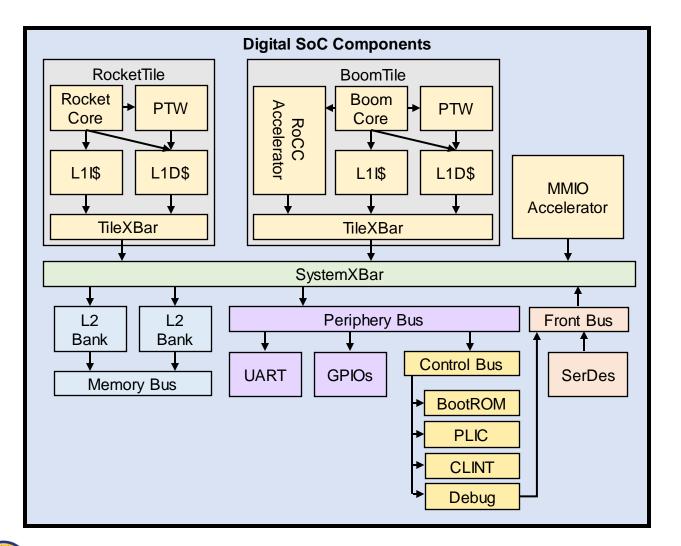

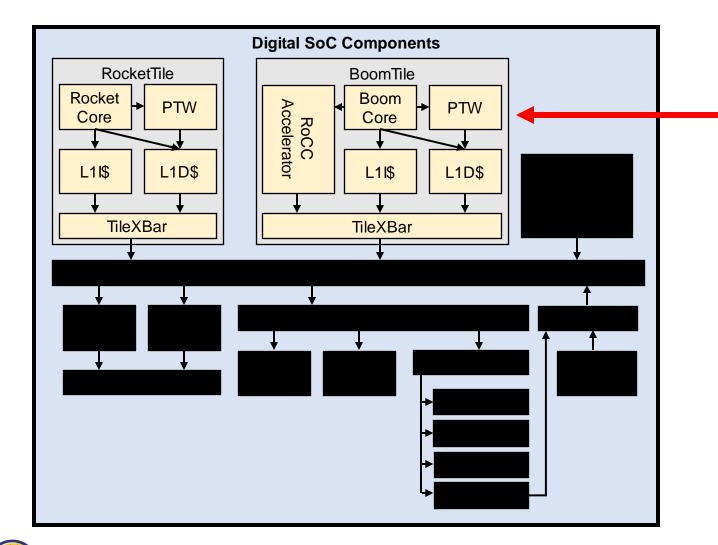

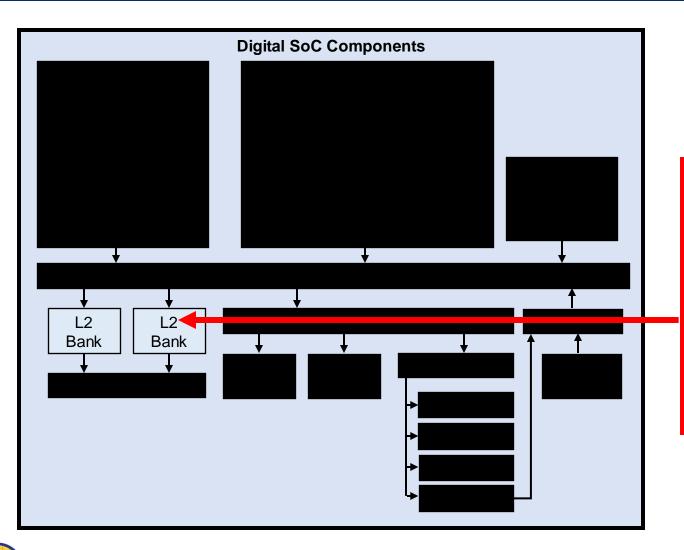

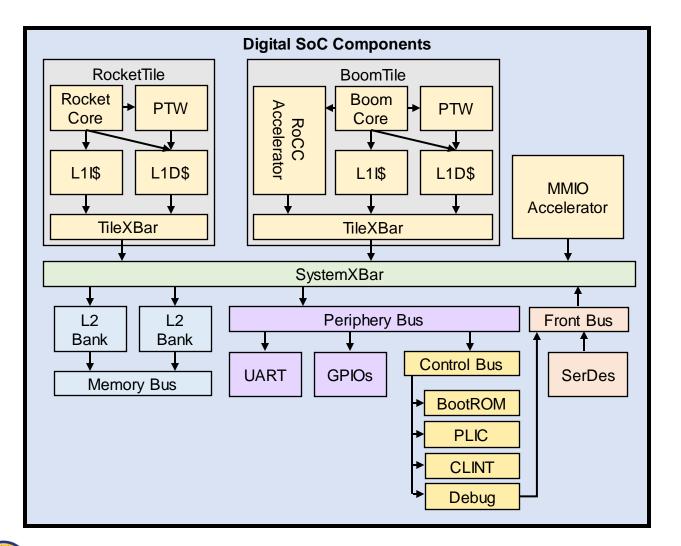

#### Tiles:

- Each Tile contains a RISC-V core and private caches

- Several varieties of Cores supported

- Interface supports integrating your own RISC-V core implementation

#### Rocket and BOOM

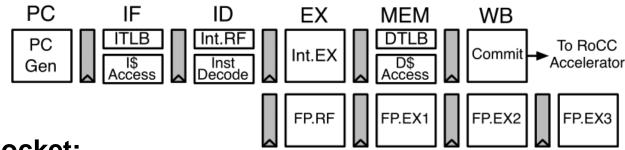

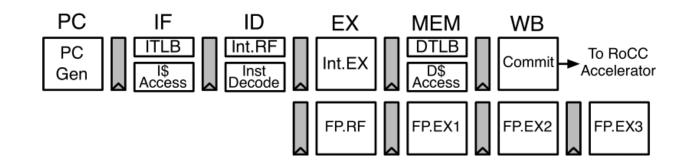

#### **Rocket:**

- First open-source RISC-V CPU

- In-order, single-issue RV64GC core

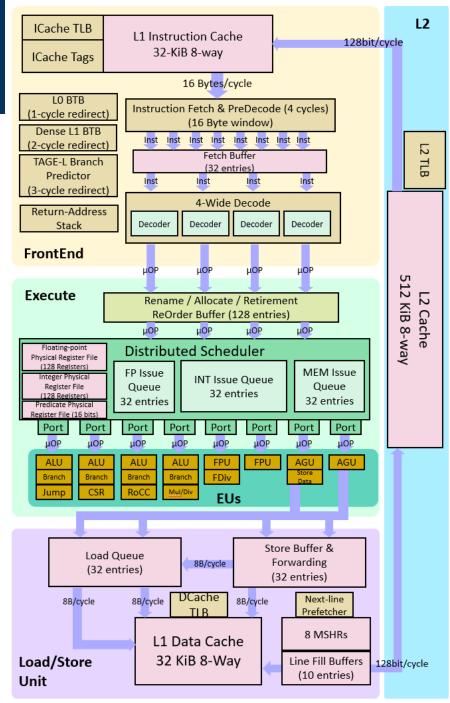

- Efficient design point for low-power devices **SonicBOOM:**

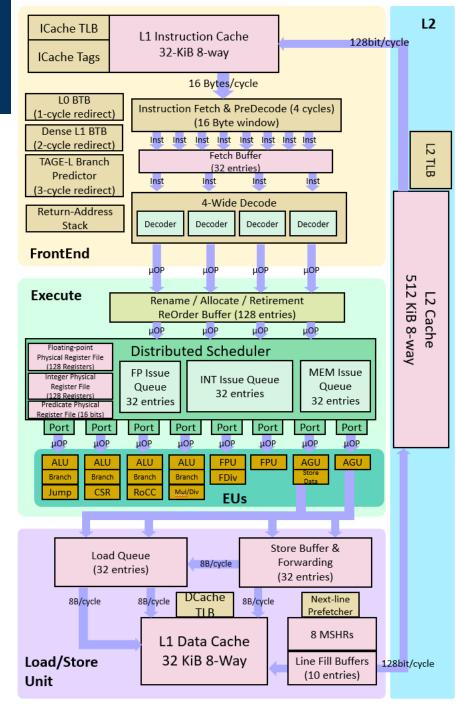

- Superscalar out-of-order RISC-V CPU

- Advanced microarchitectural features to maximize IPC

- TAGE branch prediction, OOO load-store-unit, register renaming

- High-performance design point for general-purpose systems

#### Rocket and BOOM

#### **Rocket and SonicBOOM:**

- Support RV64GC ISA profile

- Boots off-the-shelf RISC-V Linux distros (buildroot, Fedora, etc.)

- Fully synthesizable, tapeout-proven

- Described in Chisel

- Fully open-sourced

## PULP Cores in Chipyard

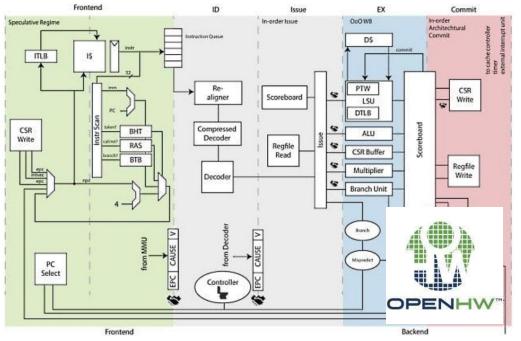

#### CVA6 (Formerly Ariane):

- RV64IMAC 6-stage single-issue in-order core

- Open-source

- Implemented in SystemVerilog

- Developed at ETH Zurich as part of PULP,

- Now maintained by OpenHWGroup

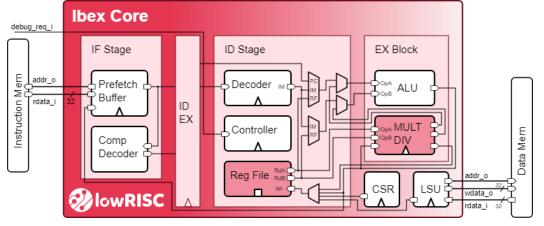

#### Ibex (Formerly Zero-RISCY):

- RV64IMC 2-stage single-issue in-order core

- Open-source

- Implemented in SystemVerilog

- Developed at ETH Zurich as part of PULP

- Now maintained by lowRISC

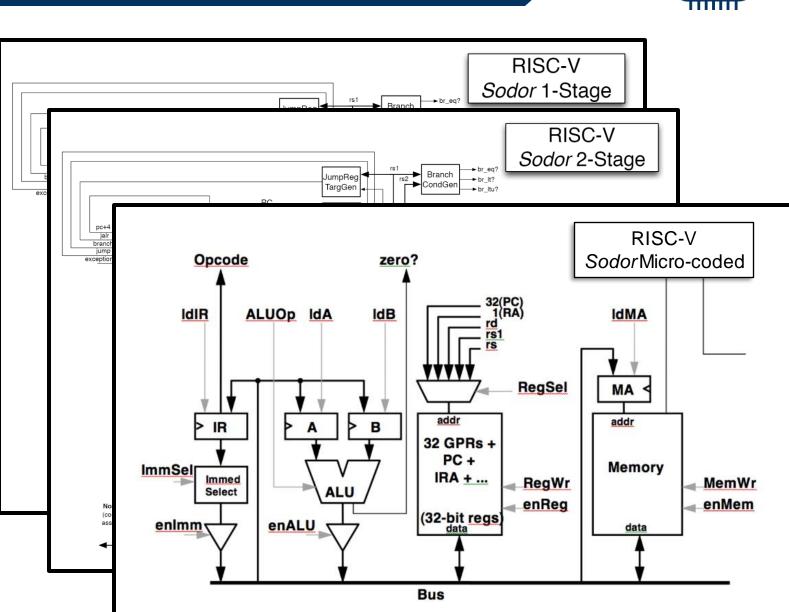

## Sodor Educational Cores

#### **Sodor Core Collection**

- Collection of RV32IM cores for teaching and education

- 1-stage, 2-stage, 3-stage, 5-stage implementations

- Micro-coded "bus-based" implementation

- Used in introductory computer architecture courses at Berkeley

Berkeley Architecture Research

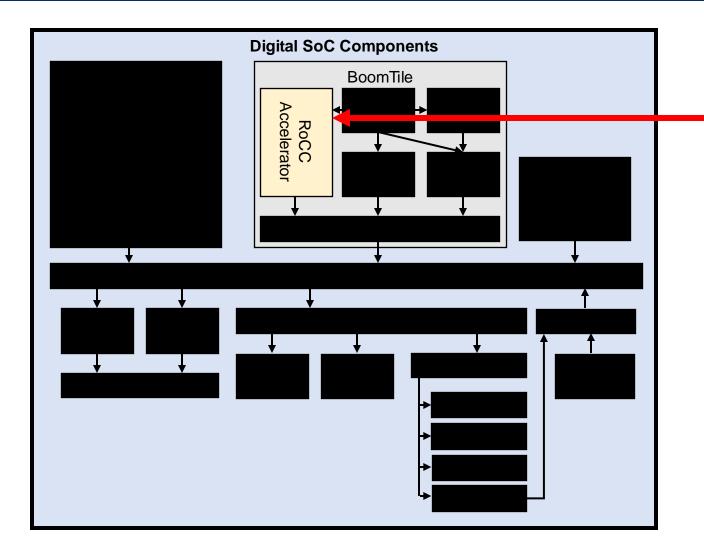

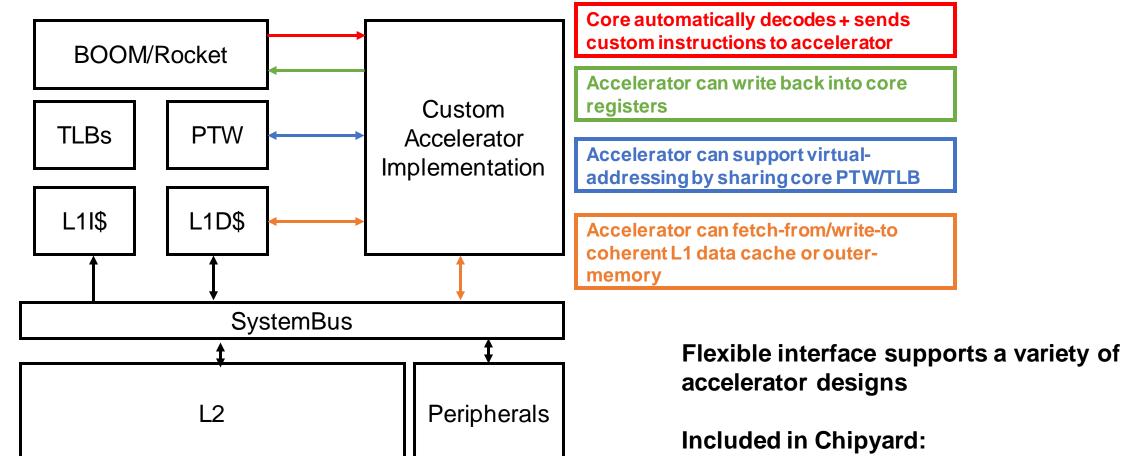

#### **RoCC Accelerators:**

- Tightly-coupled accelerator interface

- Attach custom accelerators to Rocket or BOOM cores

#### **RoCC** Accelerators

Berkeley Architecture Research

- Gemmini ML accelerator

- Hwacha vector accelerator

- SHA3 accelerator

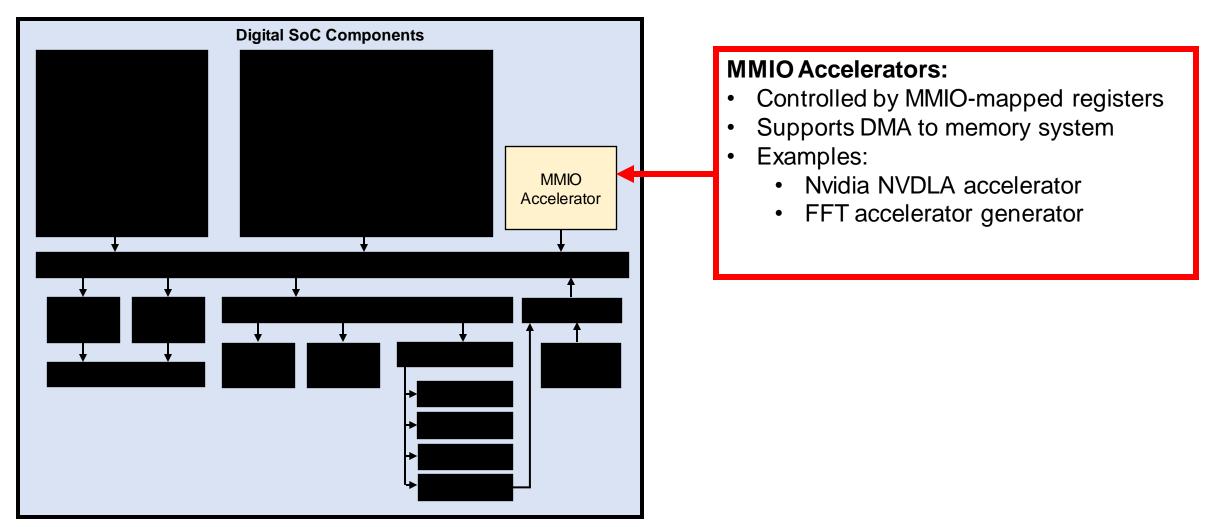

#### **MMIO** Accelerators

Berkeley Architecture Research

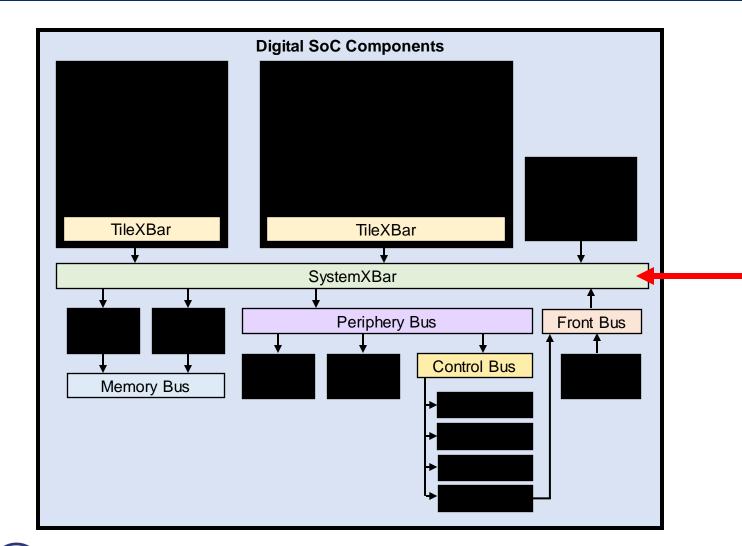

#### **TileLink Standard:**

- TileLink is open-source chip-scale interconnect standard

- Cache-coherent

- Supports multi-core, accelerators, peripherals, DMA, etc

#### Interconnect IP:

- Library of TileLink RTL generators

provided in RocketChip

- RTL generators for crossbar-based buses

- Width-adapters, clock-crossings, etc.

- Adapters to AXI4, APB

#### Shared memory:

- Open-source TileLink L2 developed by SiFive

- Directory-based coherence with MOESI-like protocol

- Configurable capacity/banking

- Support broadcast-based coherence in no-L2 systems

- Support incoherent memory systems

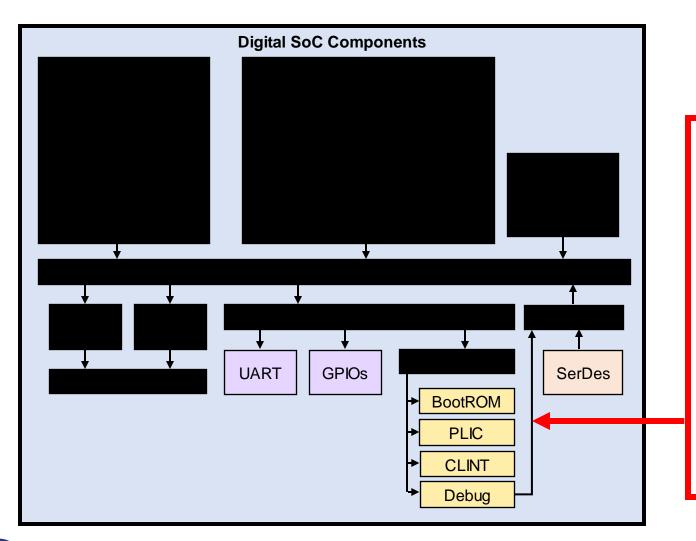

#### **Peripherals and IO:**

- Open-source RocketChip + SiFive blocks:

- Interrupt controllers

- JTAG, Debug module, BootROM

- UART, GPIOs, SPI, I2C, PWM, etc.

- TestChipIP: useful IP for test chips

- Clock-management devices

- SerDes

- Scratchpads

18

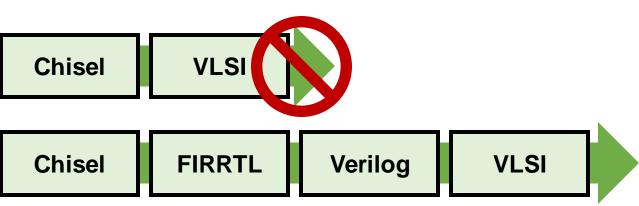

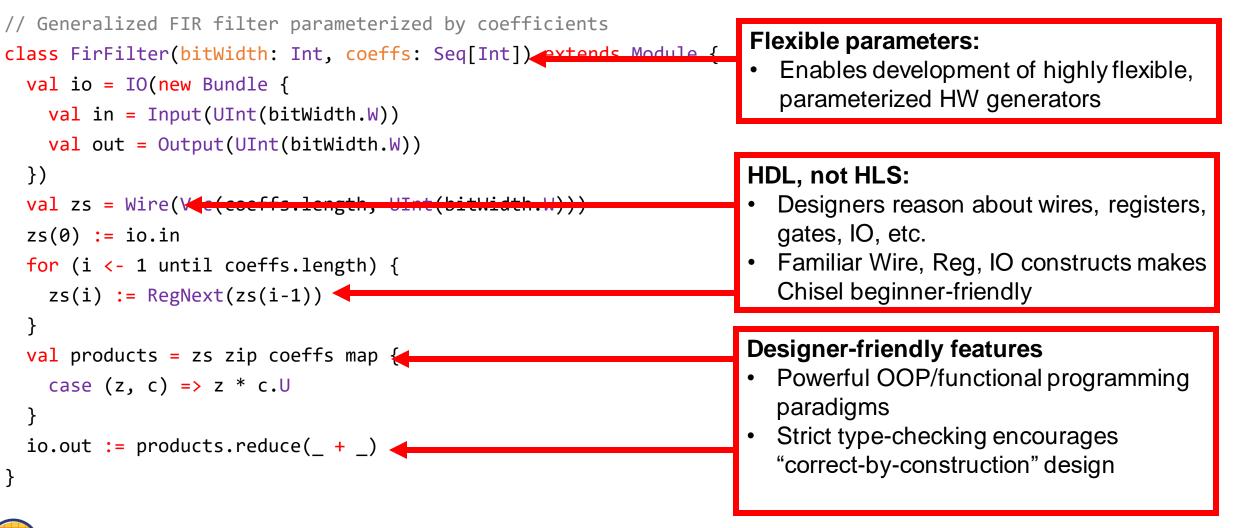

- Chisel Hardware Construction Language built on Scala

- What Chisel IS NOT:

- NOT Scala-to-gates

- NOT HLS

- NOT tool-oriented language

- What Chisel IS:

- Productive language for **generating** hardware

- Leverage OOP/Functional programming paradigms

- Enables design of parameterized generators

- Designer-friendly: low barrier-to-entry, high reward

- Backwards-compatible: integrates with Verilog black-boxes

# Chisel

### Chisel Example

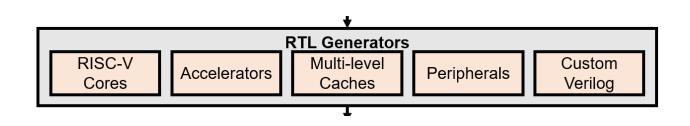

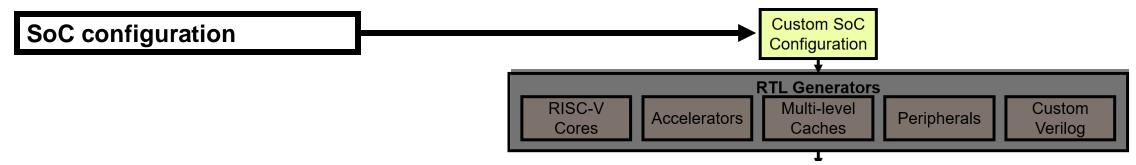

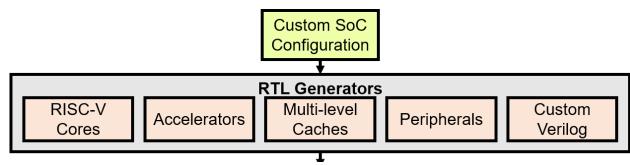

# Highly Parameterized Configurations

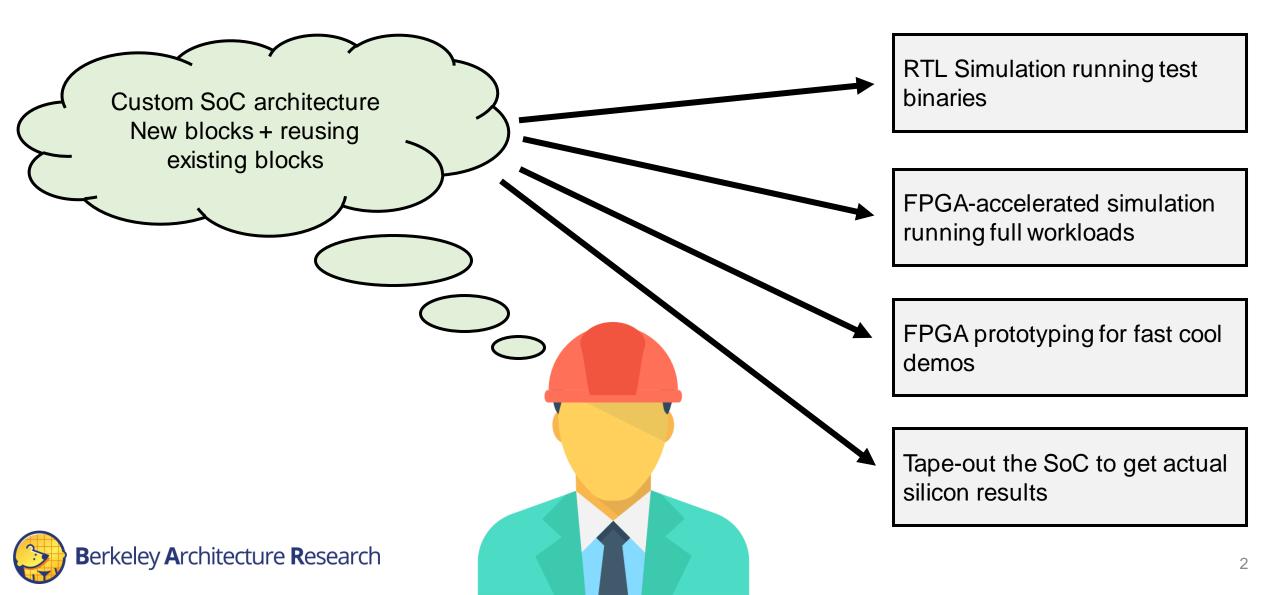

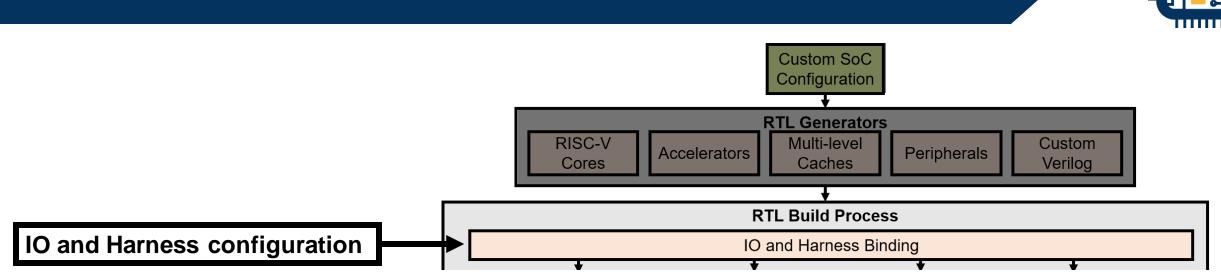

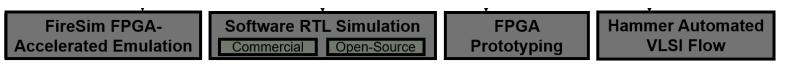

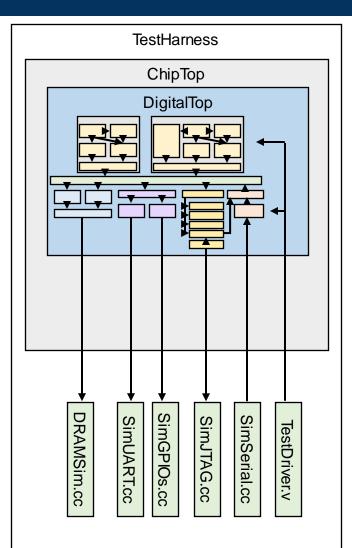

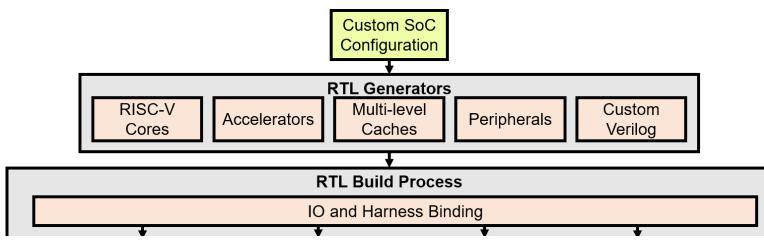

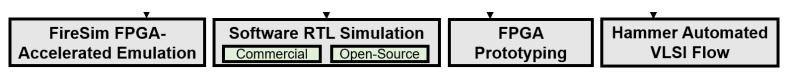

#### SW RTL Simulation:

- RTL-level simulation with Verilator or VCS

- Hands-on tutorial next

#### FPGA prototyping:

- Fast, non-deterministic prototypes

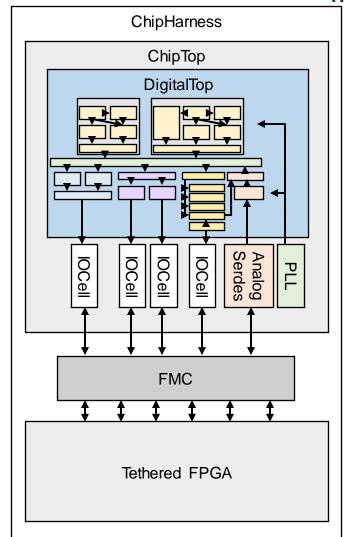

- Overview of flow later Hammer VLSI flow:

- Tapeout a custom config in some process technology

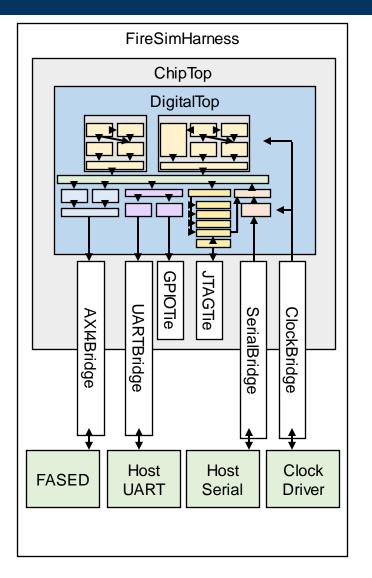

- Overview of flow later **FireSim**:

- Fast, accurate FPGAaccelerated simulations

- Hands-on tutorial later

шш

### Multipurpose

Berkeley Architecture Research

### Multipurpose

Berkeley Architecture Research

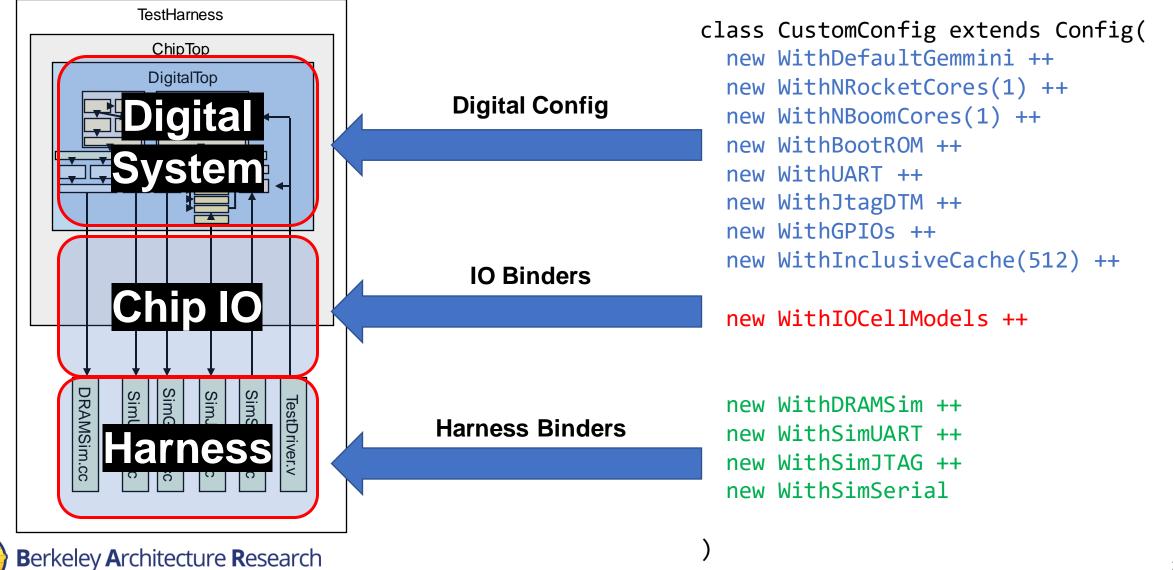

### A Complete Config

Berkeley Architecture Research

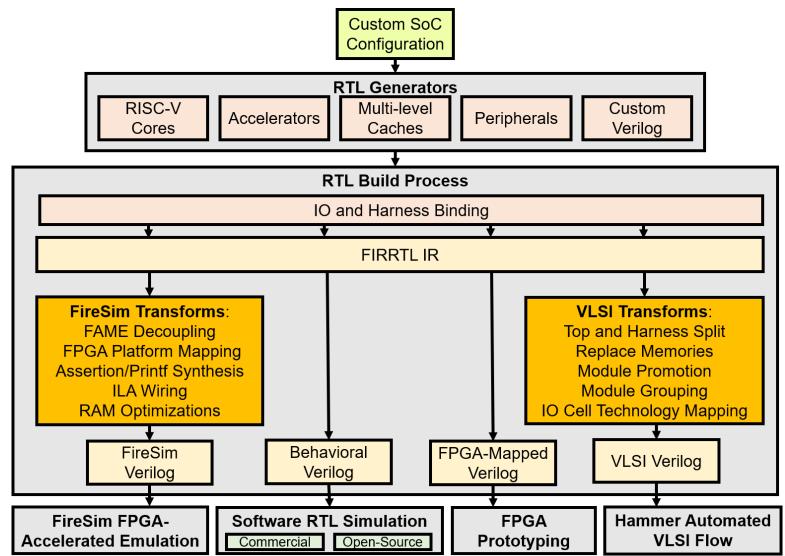

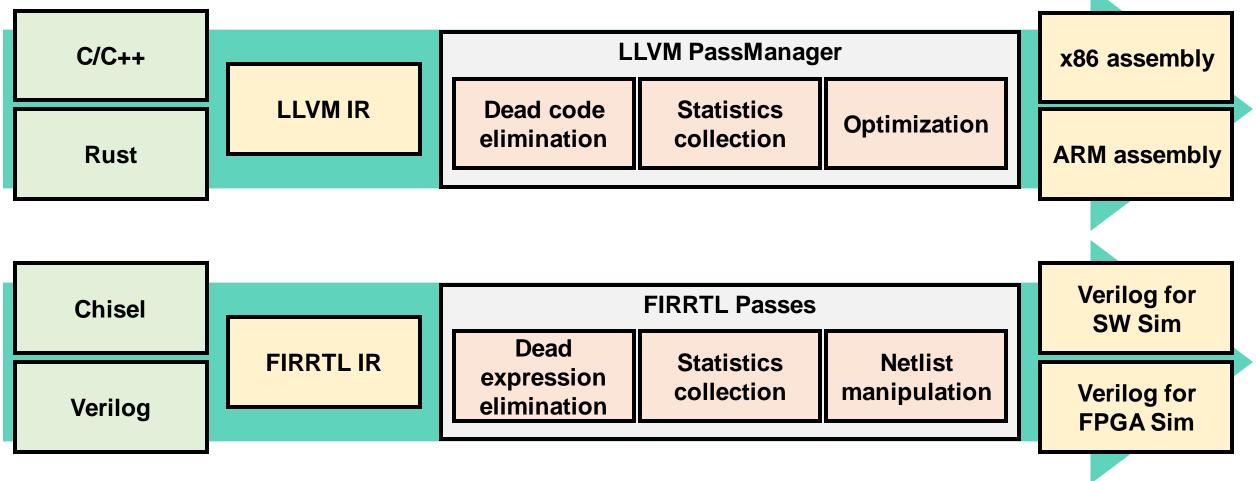

### FIRRTL – LLVM for Hardware

FIRRTL emits tool-friendly, synthesizable Verilog

Berkeley Architecture Research

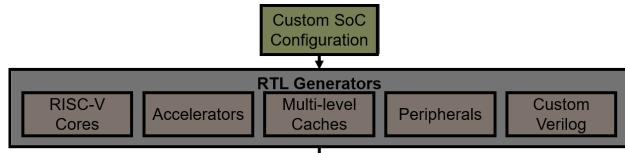

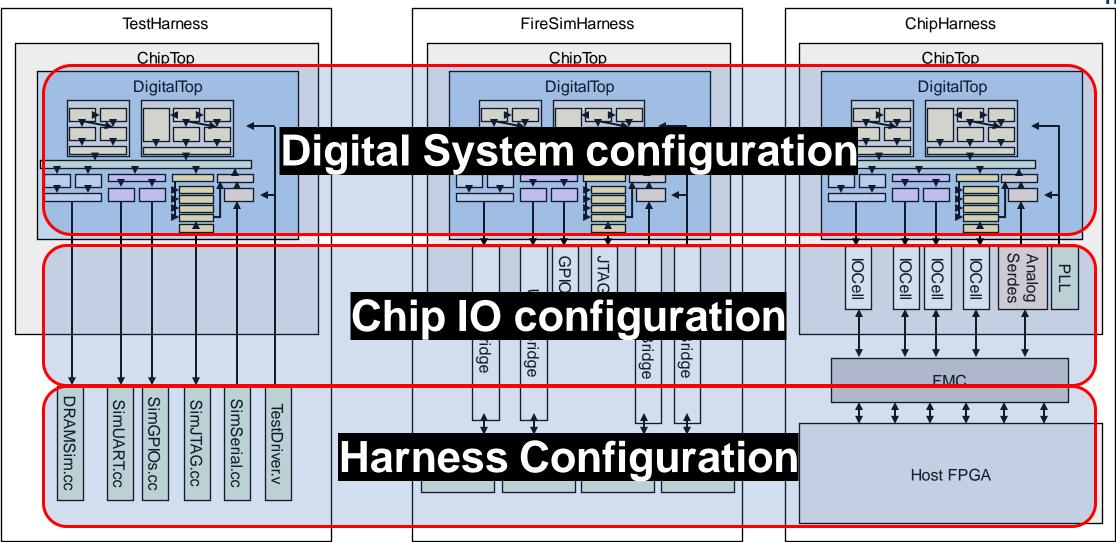

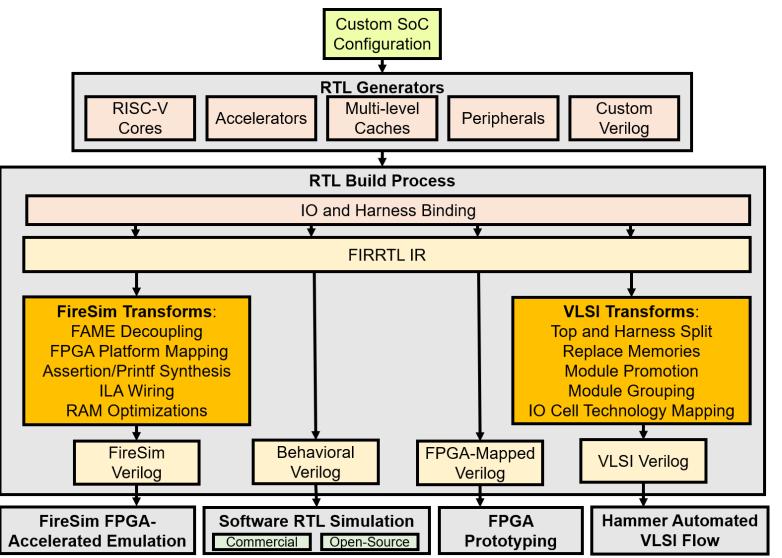

**Configs:** Describe parameterization of a multigenerator SoC

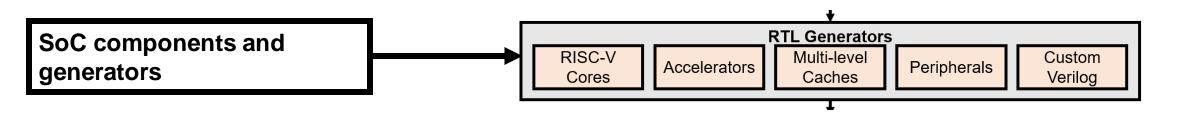

**Generators:** Flexible, reusable library of open-source Chisel generators (and Verilog too)

**IOBinders/HarnessBinders:** Enable configuring IO strategy and Harness features

**FIRRTL Passes:** Structured mechanism for supporting multiple flows

**Target flows:** Different use-cases for different types of users

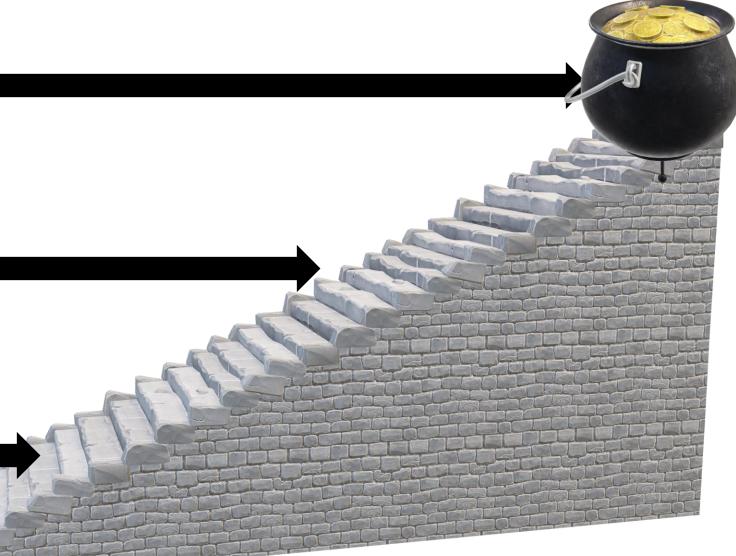

# Chipyard Learning Curve

#### Advanced-level

- Configure custom IO/clocking setups

- Develop custom FireSim extensions

- Integrate and tape-out a complete SoC

#### **Evaluation-level**

- Integrate or develop custom hardware IP into Chipyard

- Run FireSim FPGA-accelerated simulations

- Push a design through the Hammer VLSI flow

- Build your own system

#### **Exploratory-level**

- Configure a custom SoC from pre-existing components

- Generate RTL, and simulate it in RTL level simulation

- Evaluate existing RISC-V designs

Berkeley Architecture Research

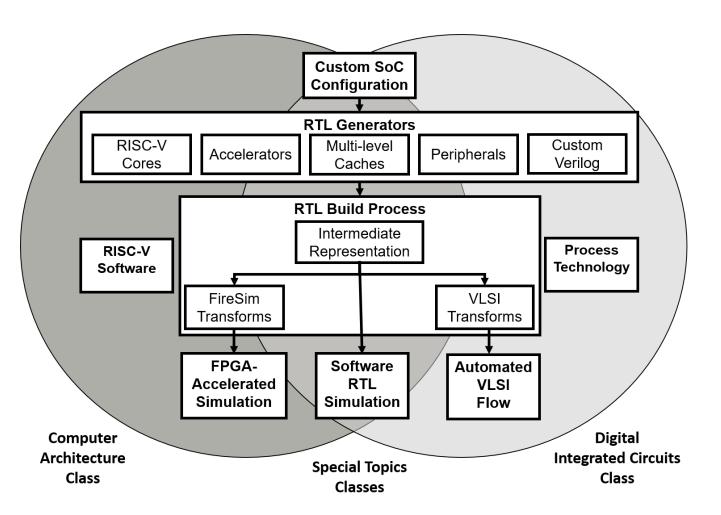

### **Chipyard is Education Friendly**

Proven in many Berkeley Architecture courses

- Hardware for Machine Learning

- Undergraduate Computer Architecture

- Graduate Computer Architecture

- Advanced Digital ICs

- Tapeout HW design course

Advantages of common shared HW framework

- Reduced ramp-up time for students

- Students learn framework once, reuse it in later courses

- Enables more advanced course projects (tapeout a chip in 1 semester)

Berkeley Engineering students pull off novel chip design in a single semester. The class shows successful model for expanding entry into field of semiconductor design

#### Berkeley engineering students pull off novel chip design in a single semester

Class shows successful model for expanding entry into field of semiconductor design

36

### Chipyard is Research-Friendly

- Add new accelerators/custom instructions

- Modify OS/driver/software

- Perform design-space exploration across many parameters

- Test in software and FPGA-sim before tape-out

# Chipyard is Community-Friendly

#### **Documentation:**

- https://chipyard.readthedocs.io/en/dev/

- 133 pages

- Most of today's tutorial content is covered there

#### Mailing List:

• google.com/forum/#!forum/chipyard

#### **Open-sourced:**

- All code is hosted on GitHub

- Issues, feature-requests, PRs are welcomed

Docs » Welcome to Chipyard's documentation!

G Edit on GitHub

#### Welcome to Chipyard's documentation!

Chipyard is a framework for designing and evaluating full-system hardware using agile teams. It is composed of a collection of tools and libraries designed to provide an integration between open-source and commercial tools for the development of systems-on-chip.

#### Important

New to Chipyard? Jump to the Initial Repository Setup page for setup instructions.

### Conclusion

- **Chipyard:** An open, extensible research and design platform for RISC-V SoCs

- Unified framework of parameterized generators

- One-stop-shop for RISC-V SoC design exploration

- Supports variety of flows for multiple use cases

- Open-sourced, community and research-friendly

#### **Questions?**